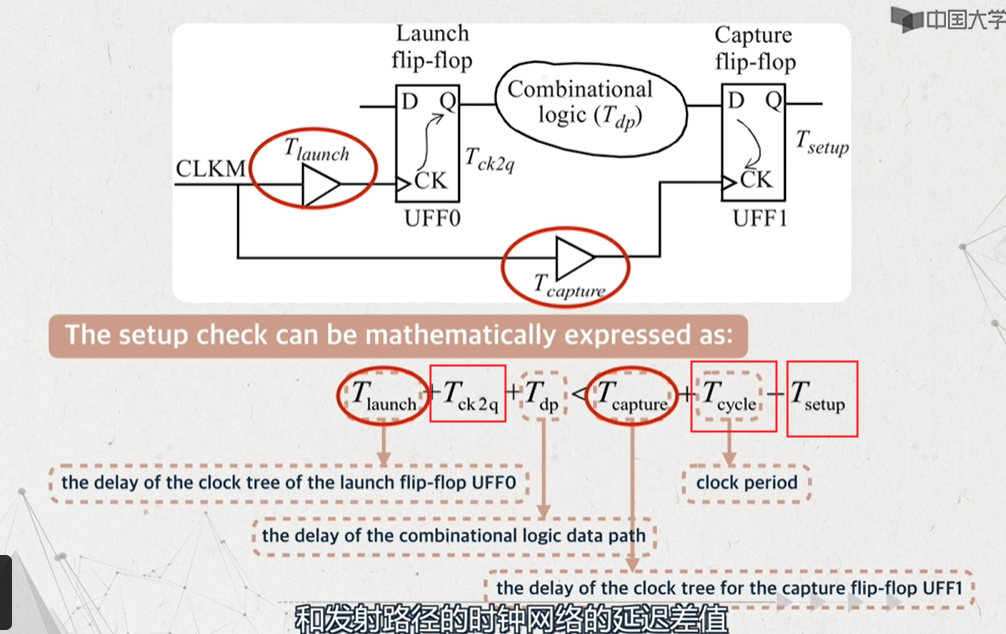

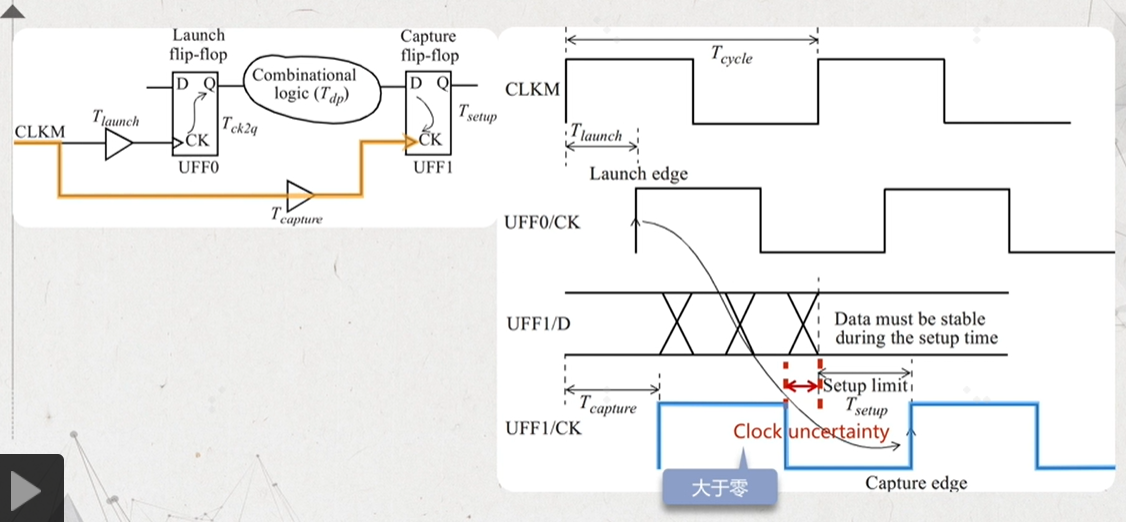

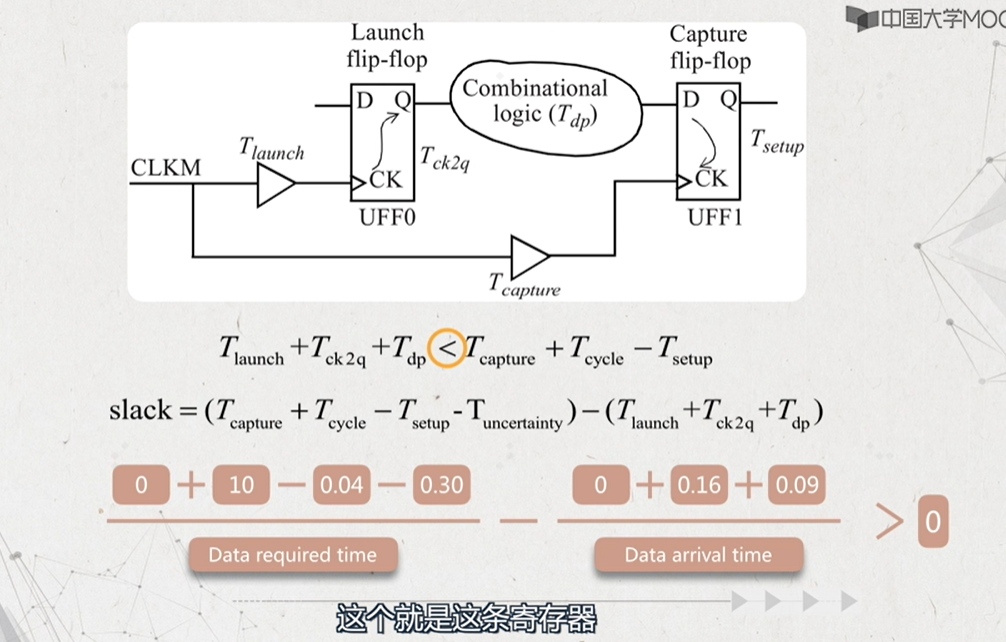

`T(launch)`和`T(capture)`的差值很小。

`T(cycle)`在设计电路的时候已经定义好了。

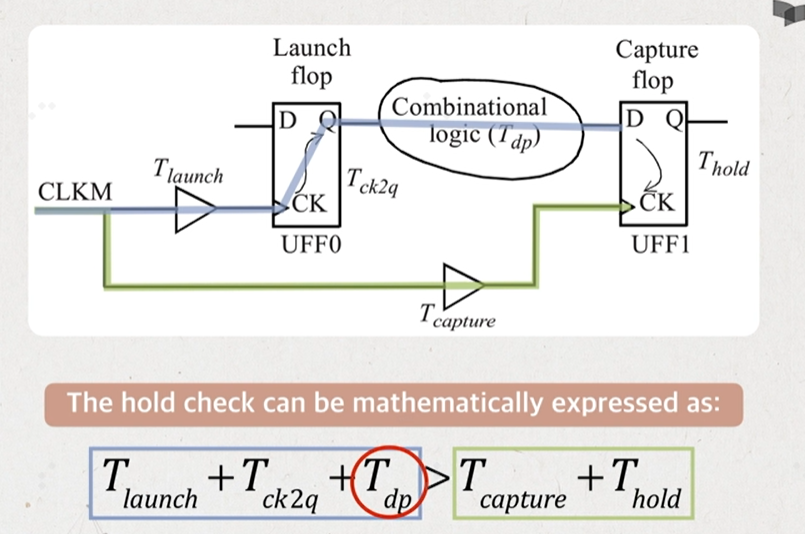

`T(ck2q)`D触发器的时钟端口到Q端的延时,和D触发器的的建立时间 `T(setup)`是确定的,对于固定的工艺库来说,

唯一可变的是组合逻辑的延时

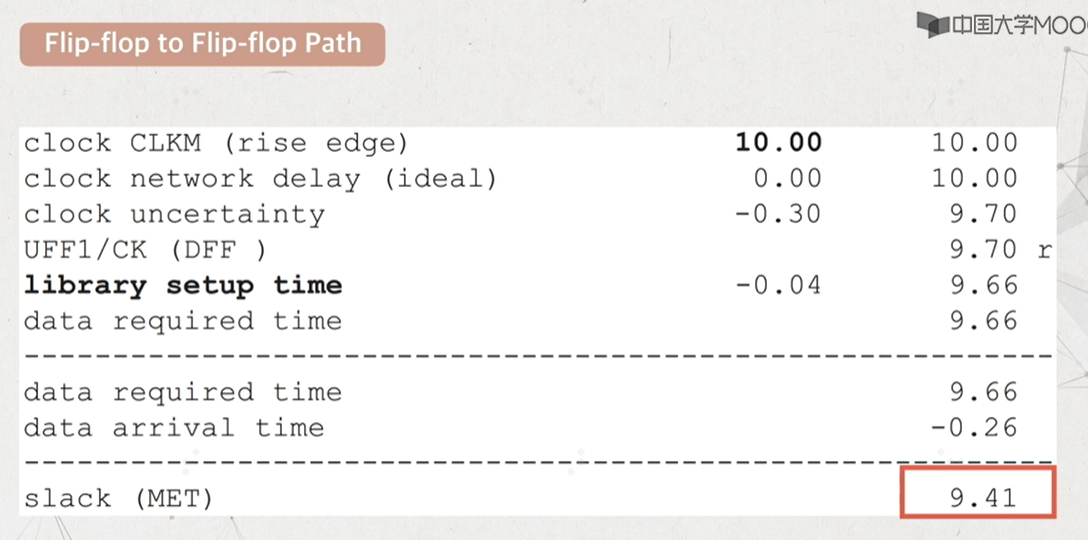

max说明的建立时间的检查

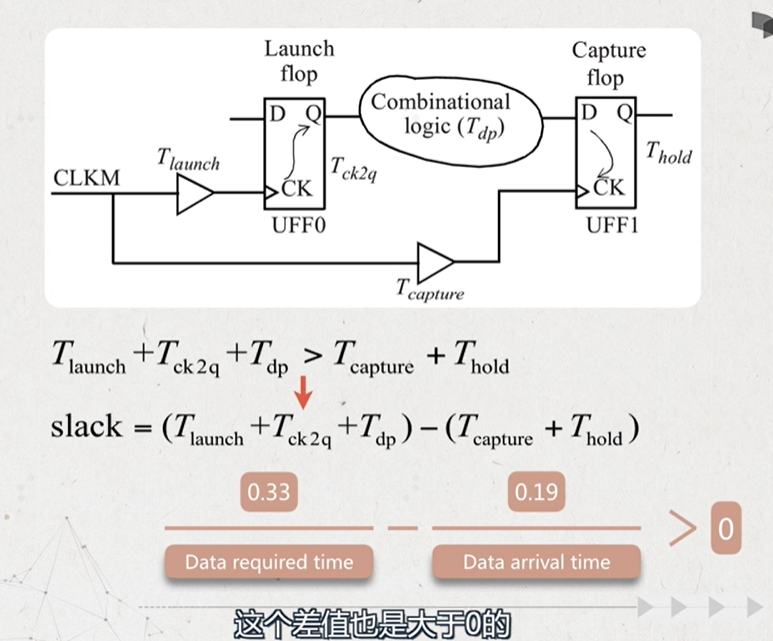

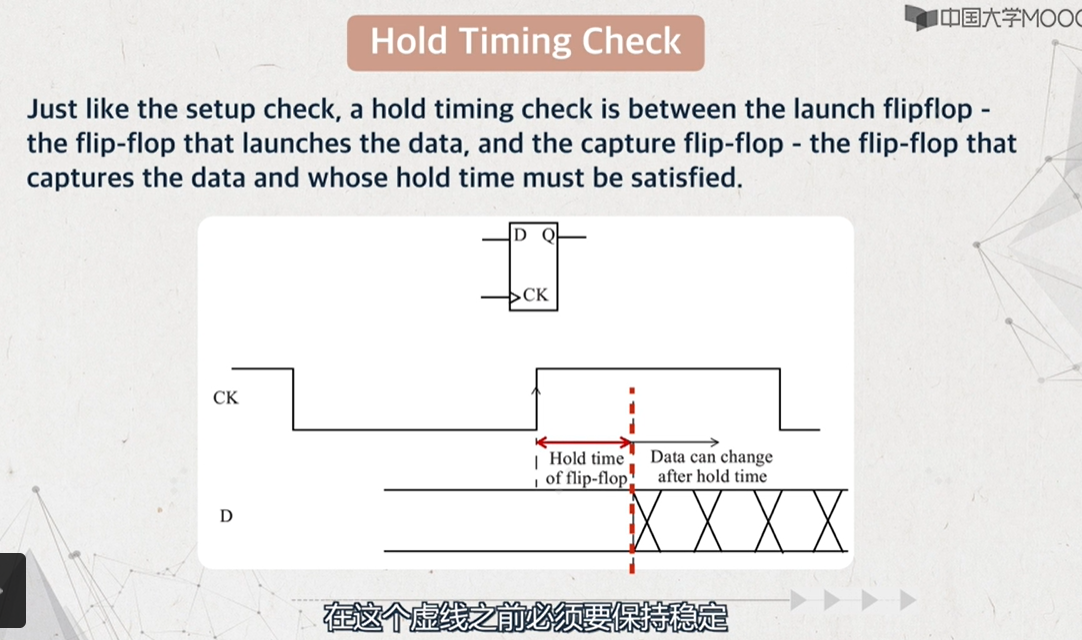

min是保持时间的检查

从内核端口到触发器的延迟叫时钟网络延时。

时钟从其原点传播到正在分析的设计的时钟定义点所需的时间为clock_lantency.

**保持时间,他的发射时钟边沿和捕获时钟边沿都是同一个边沿**