### 二级D触发器应用于同步器,减少亚稳态

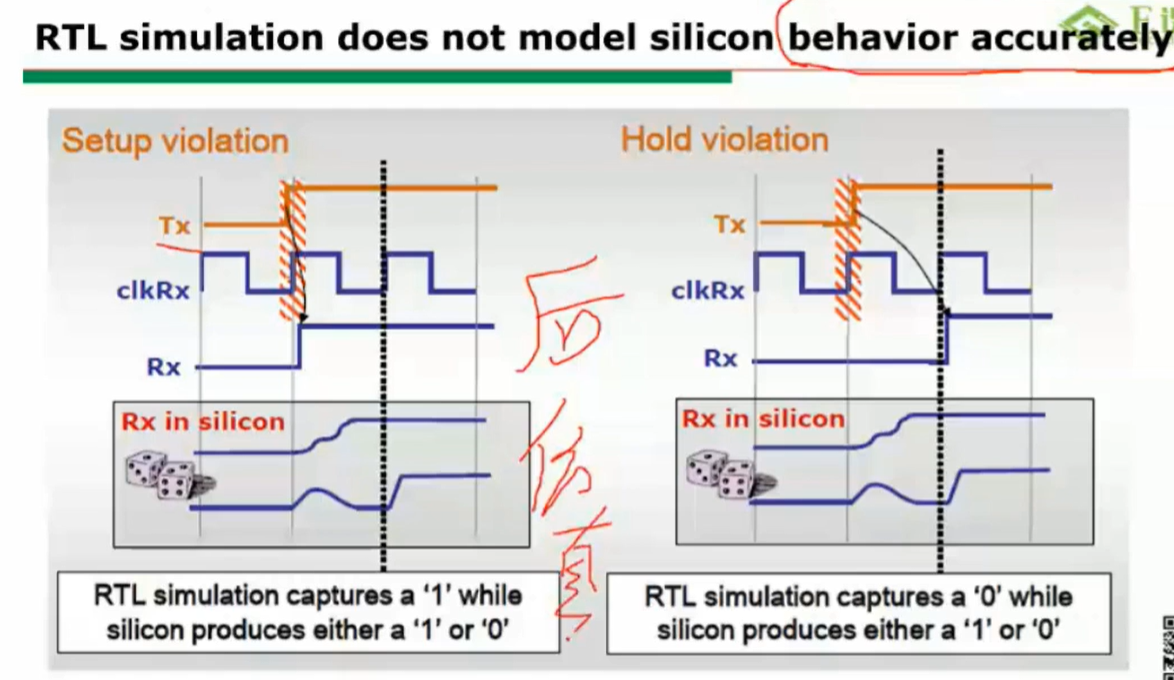

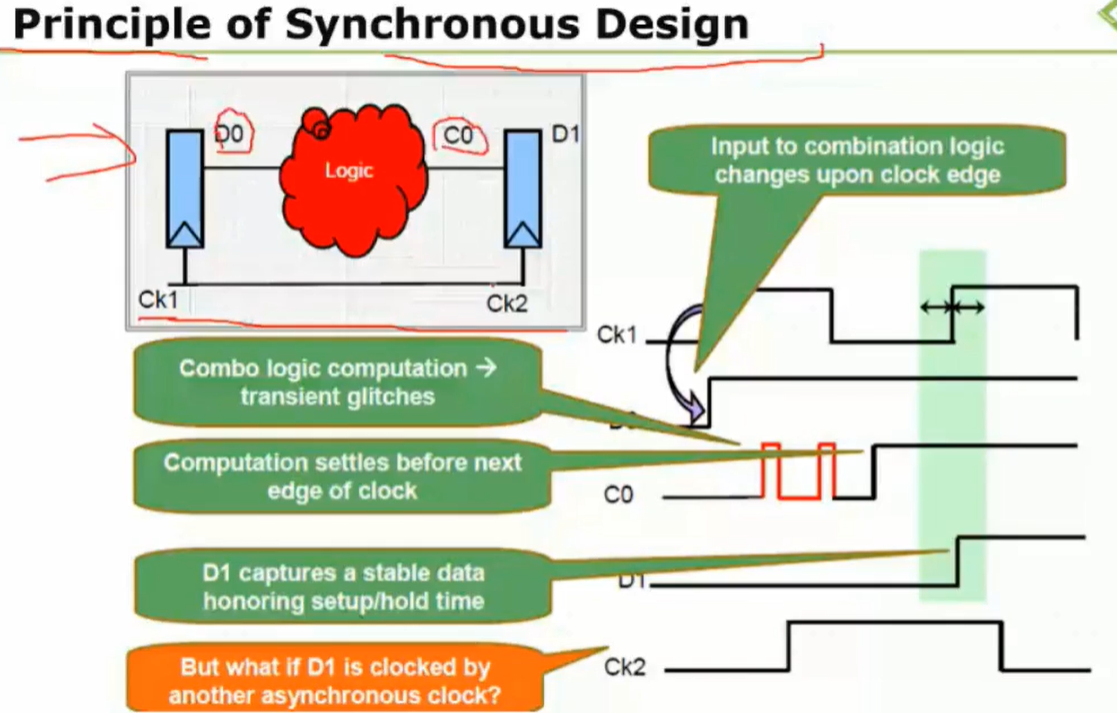

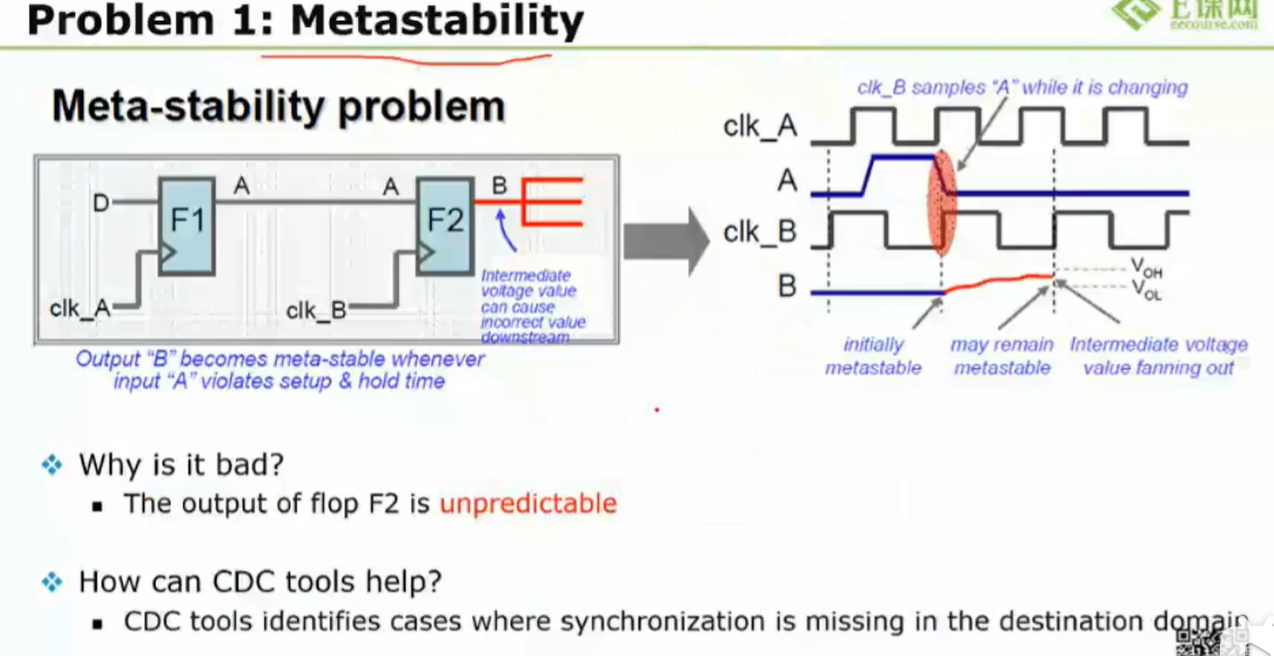

**建立时间**(Tsu:set up time)是指在时钟沿到来之前数据从不稳定到稳定所需的时间,如果建立的时间不满足要求那么数据将不能在这个时钟上升沿被稳定的打入触发器;

**保持时间**(Th:hold time)是指数据稳定后保持的时间,如果保持时间不满足要求那么数据同样也不能被稳定的打入触发器。

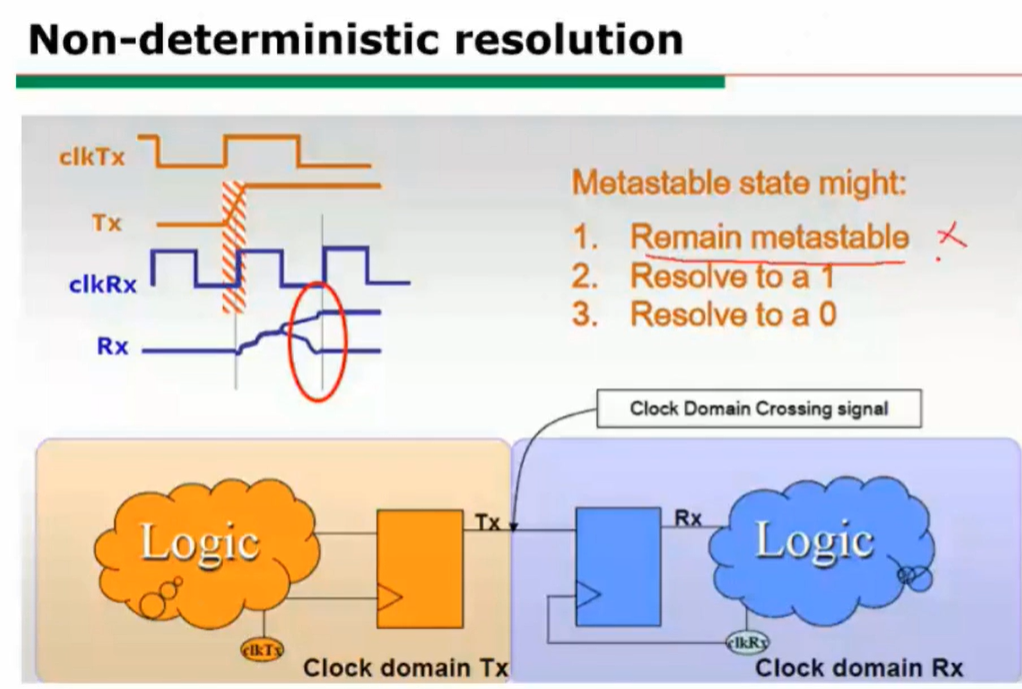

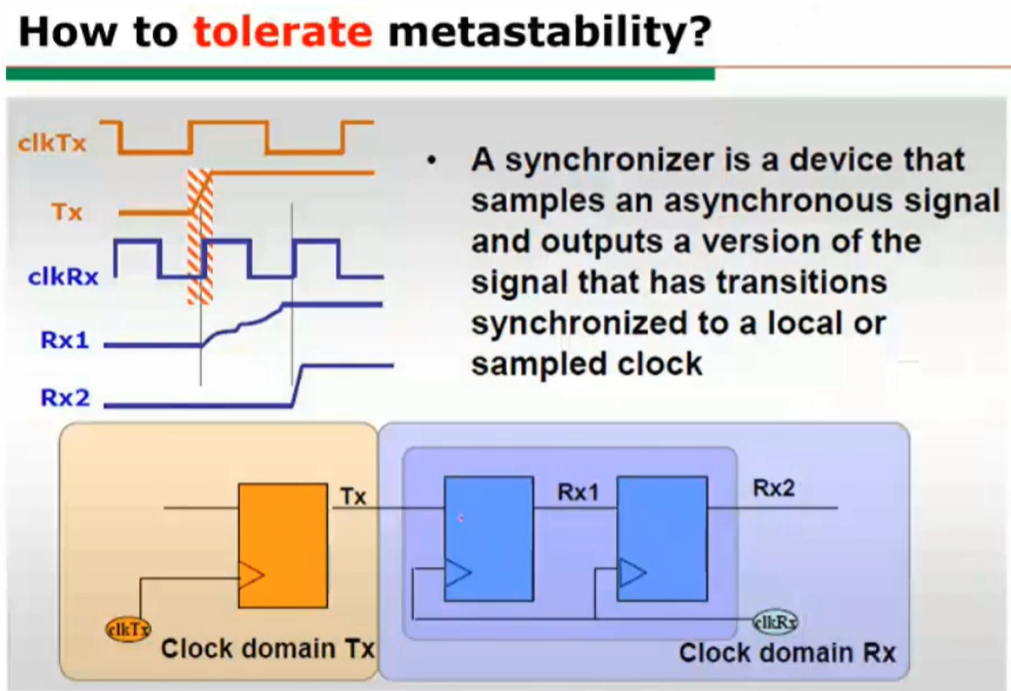

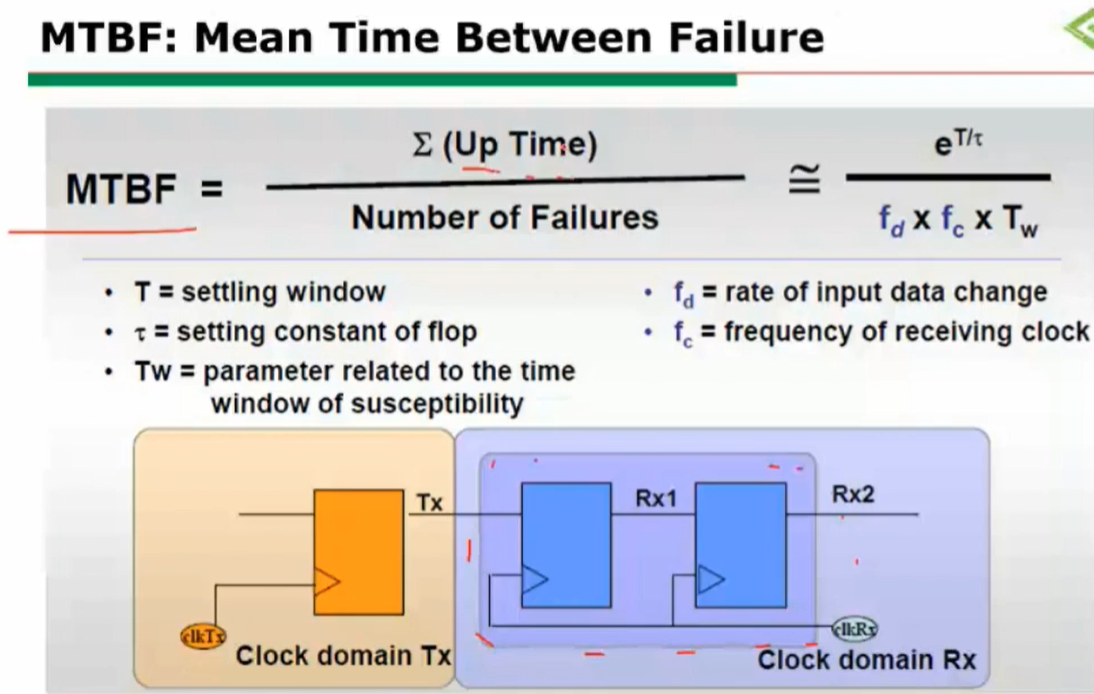

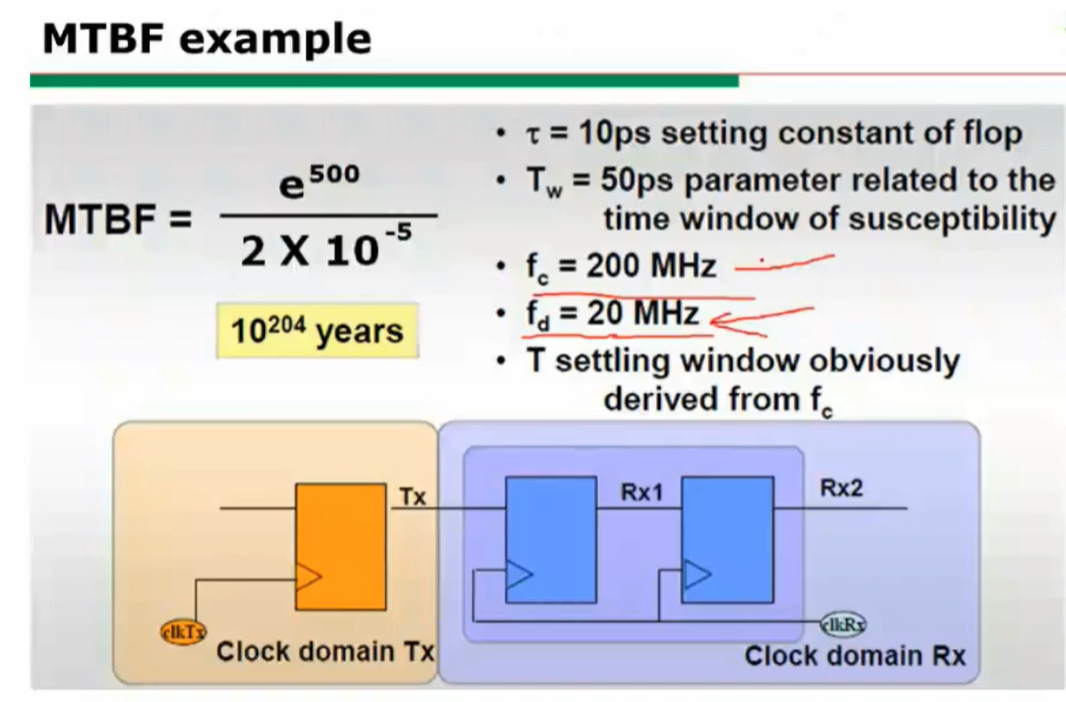

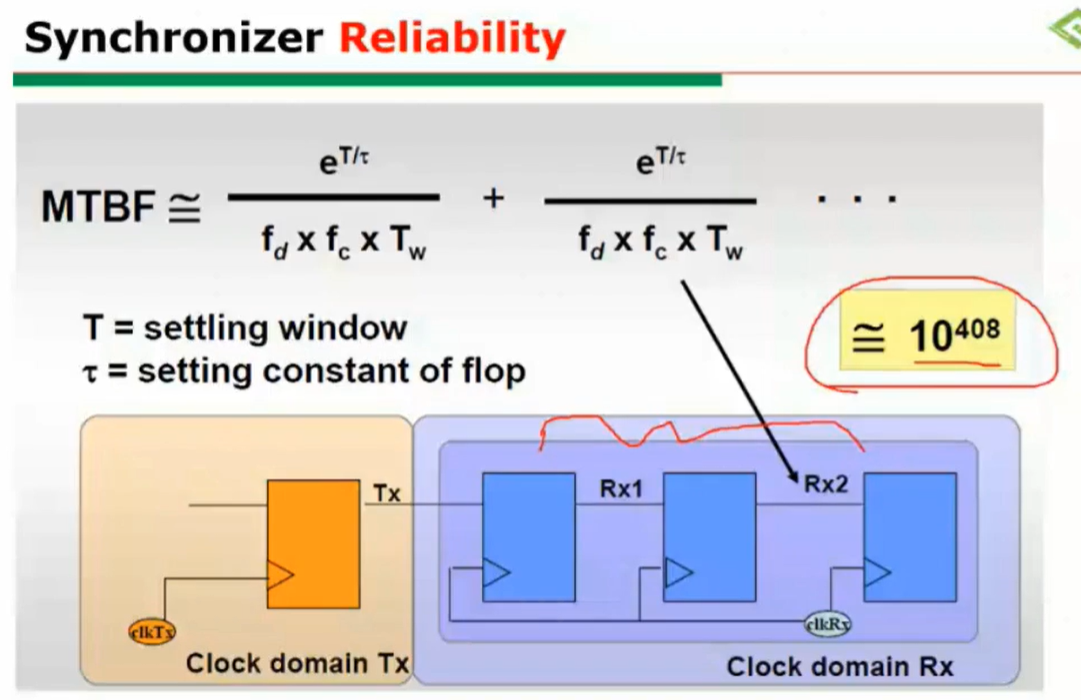

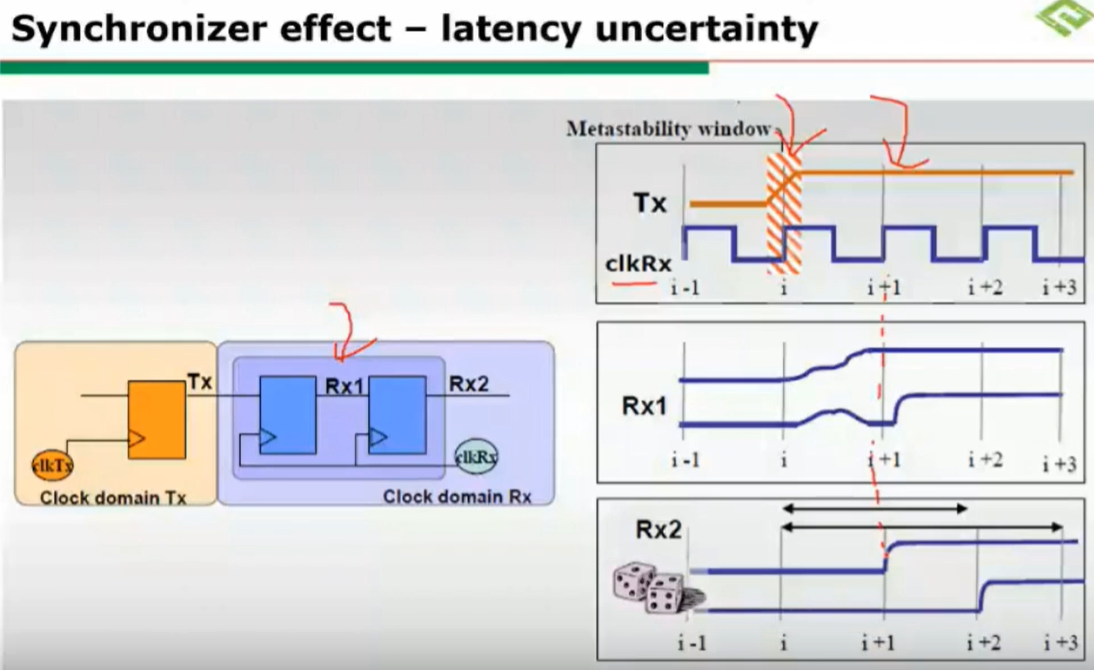

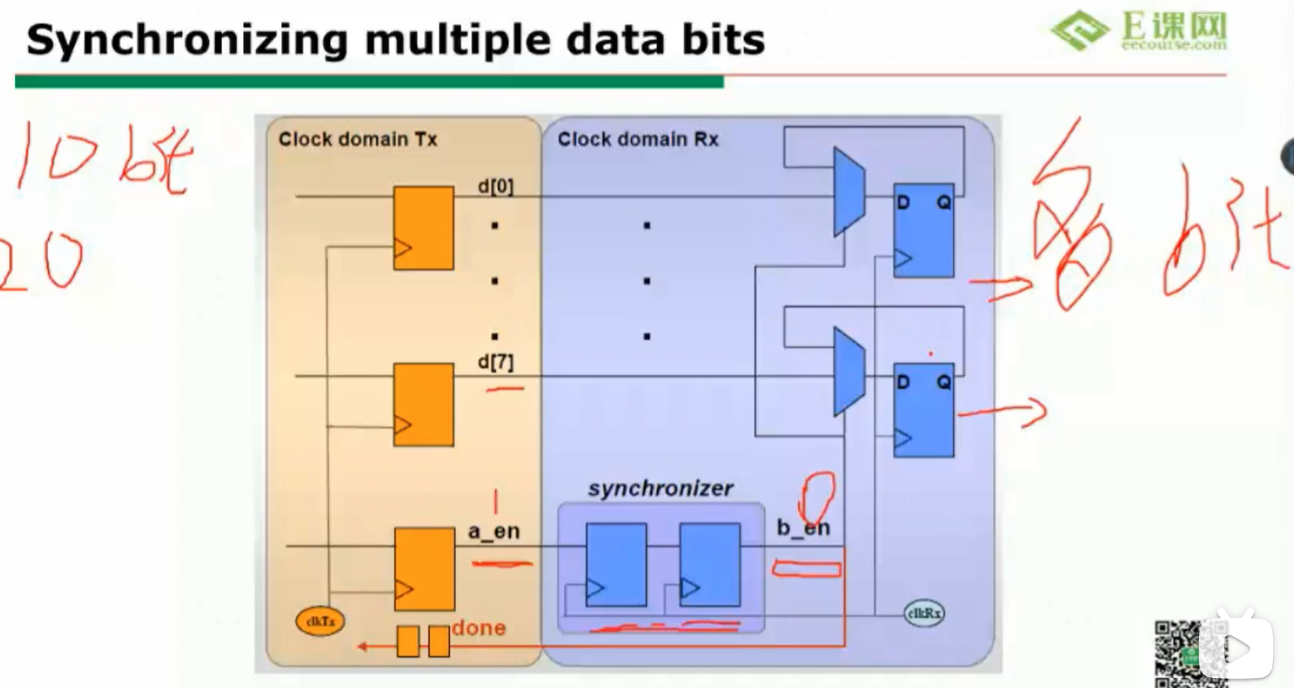

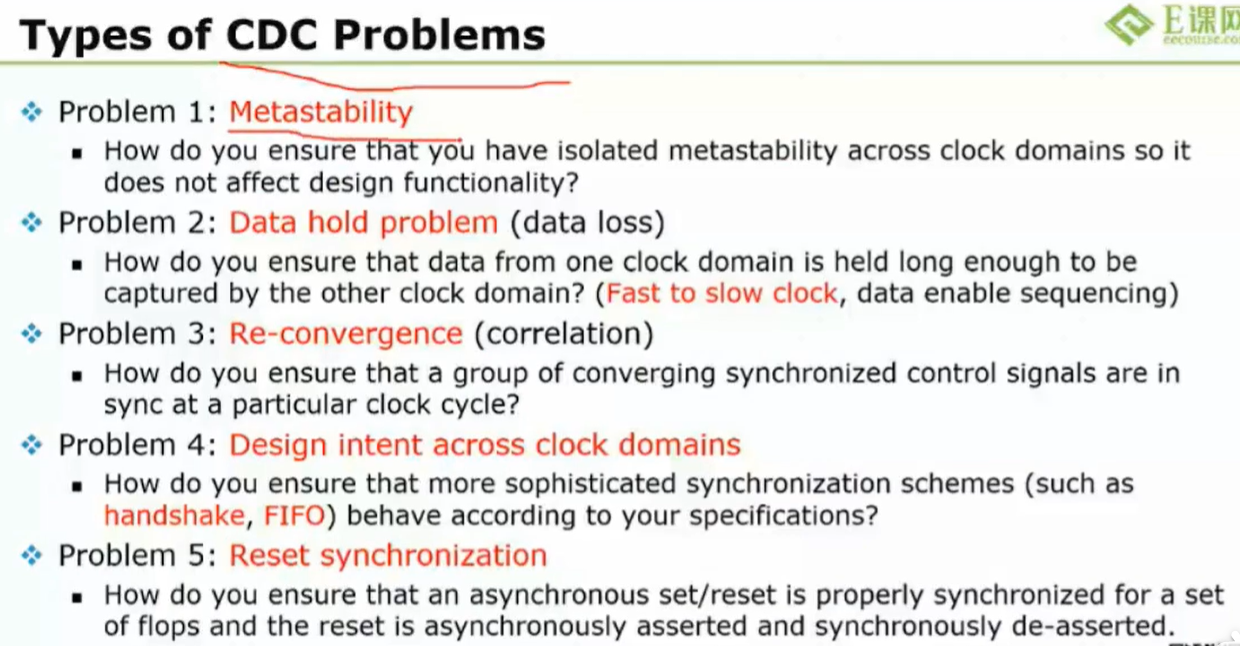

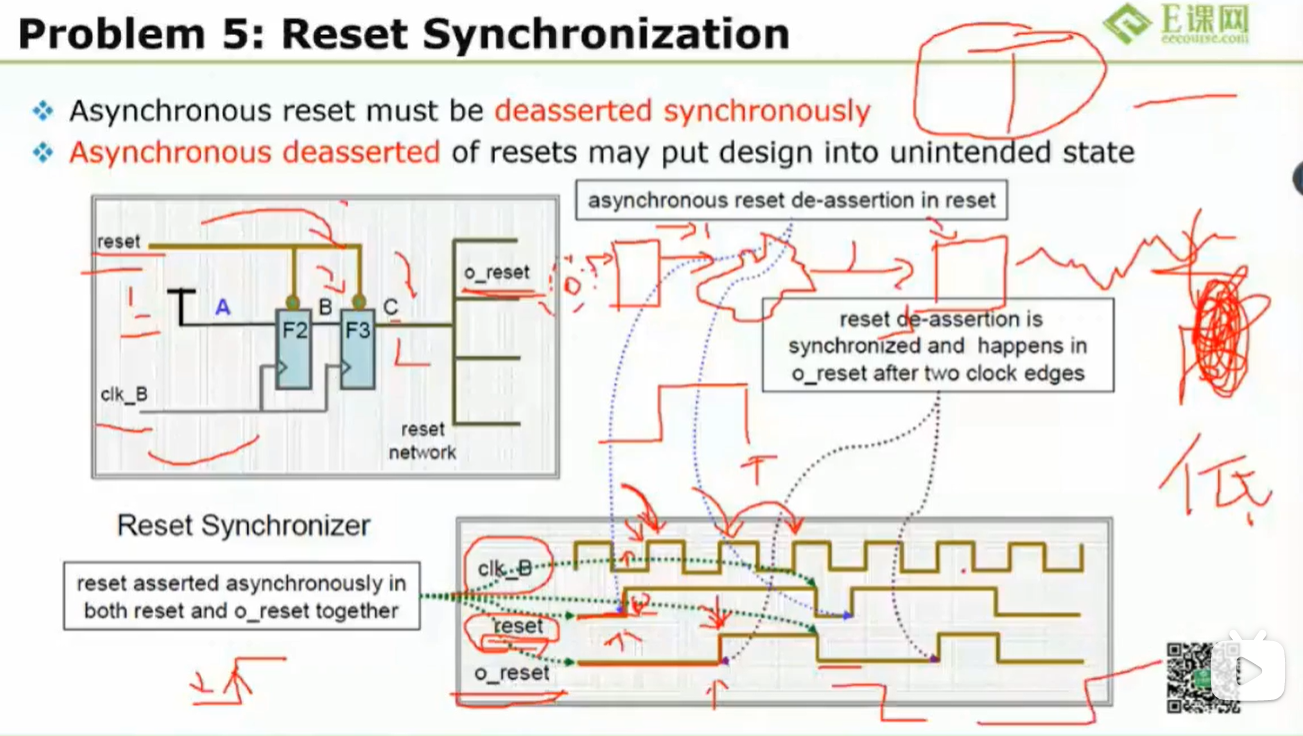

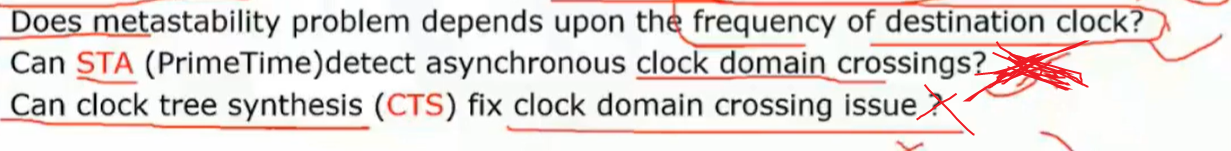

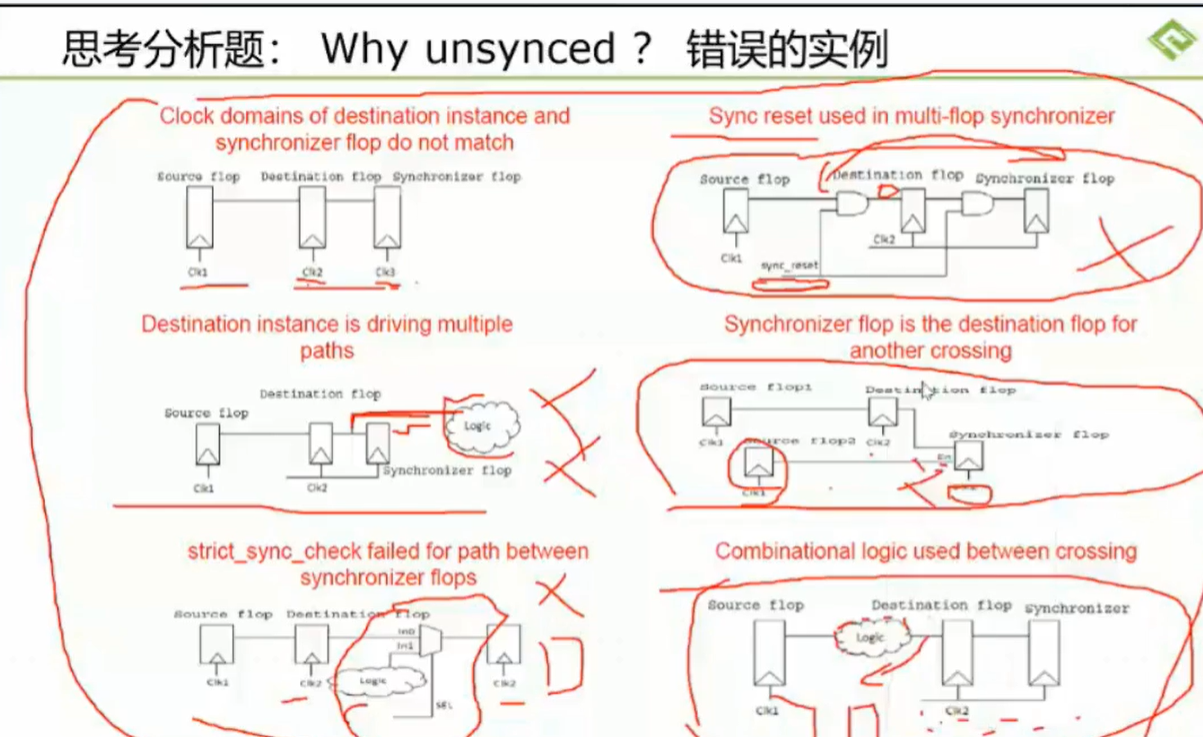

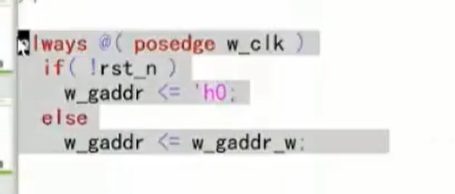

当第一级触发器采样异步输入之后,允许输出出现的亚稳态可以长达一个周期,**在这个周期内,亚稳态特性减弱**。在第二个时钟沿到来时,第二级同步器采样,之后才把该信号传递到内部逻辑中去。**第二级输出是稳定且已被同步了的。如果在第二级采样时保持时间不够,第一级的输出仍然处于很强的亚稳态,将会导致第二级同步器也进入亚稳态,但这种故障出现的概率比较小。**

一般情况下,两级同步器总体的故障概率是一级同步器故障概率的平方。**在大部分的同步化设计中,两级同步器足以消除所有可能的亚稳态了。**

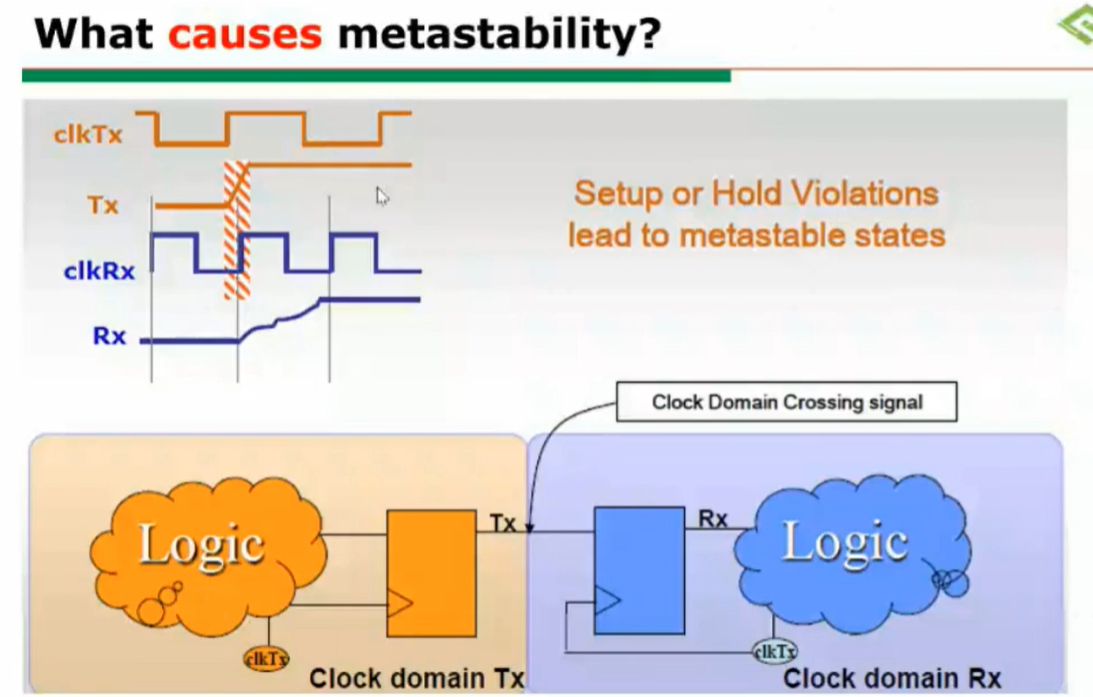

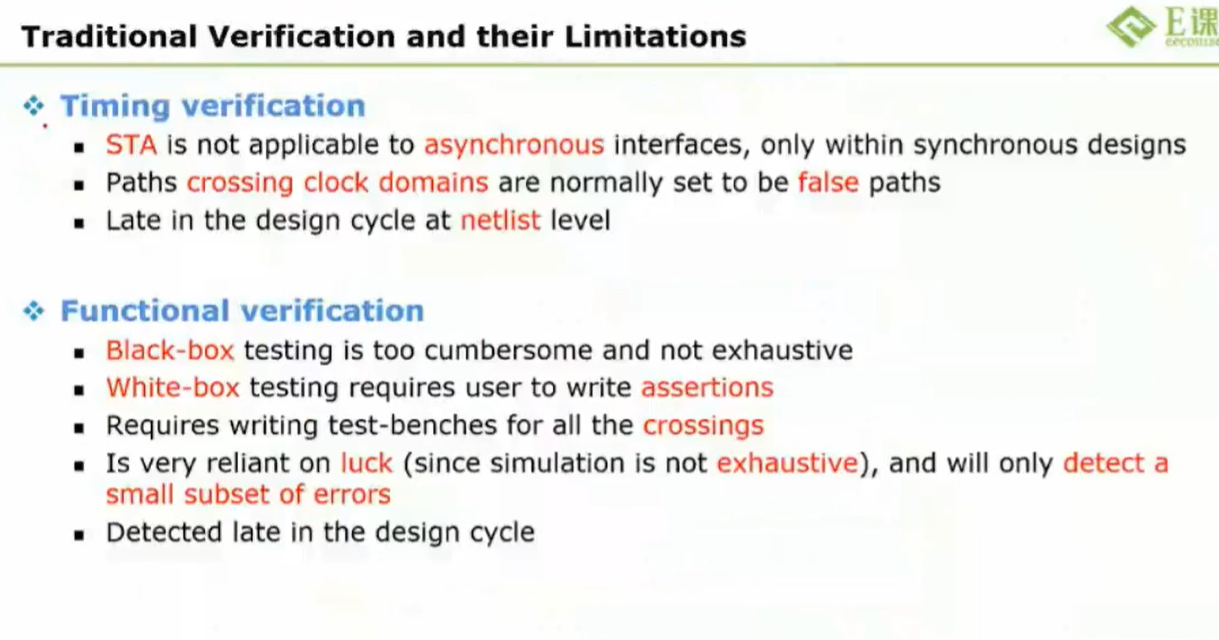

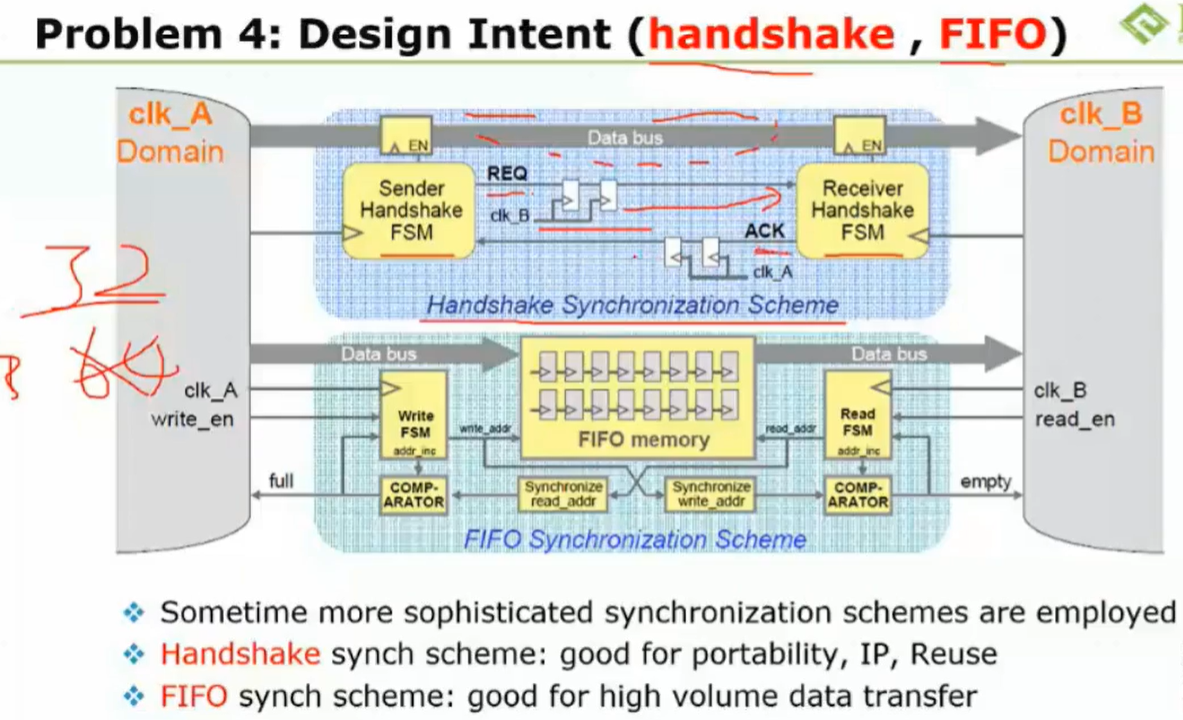

synchronous有一个时钟域,

asynchronous 有多个时钟域,会出现跨时钟域的问题

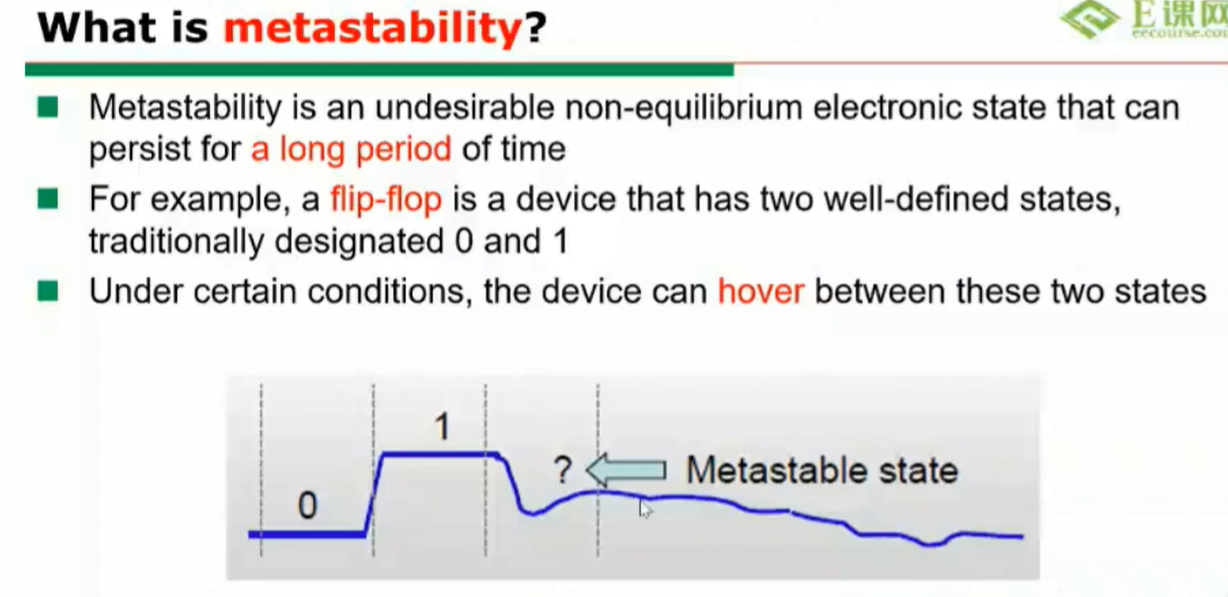

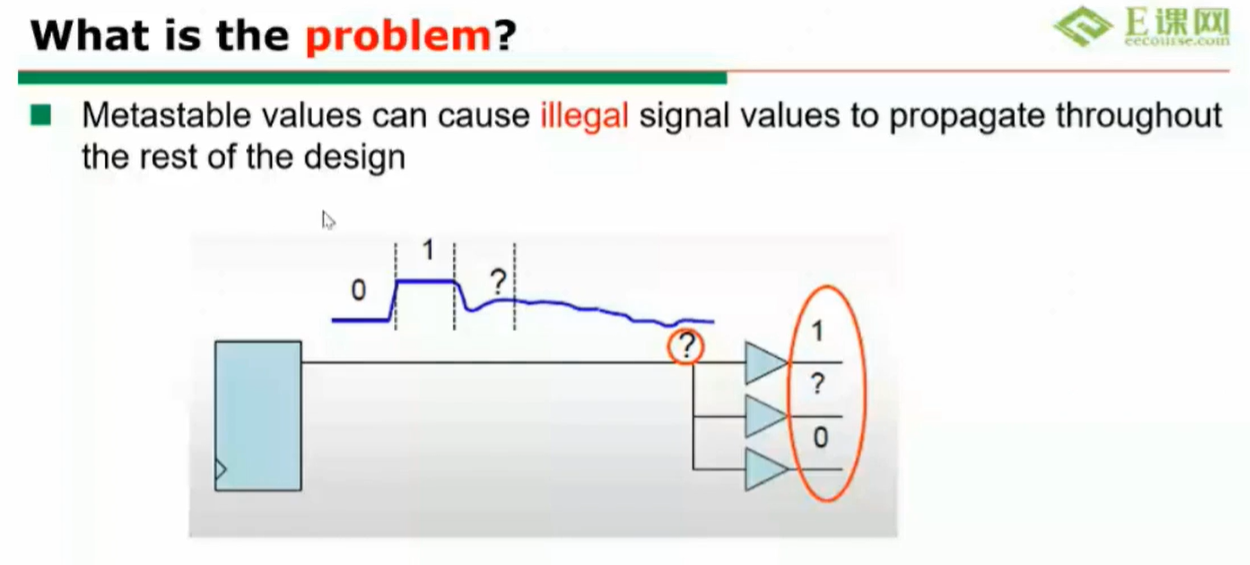

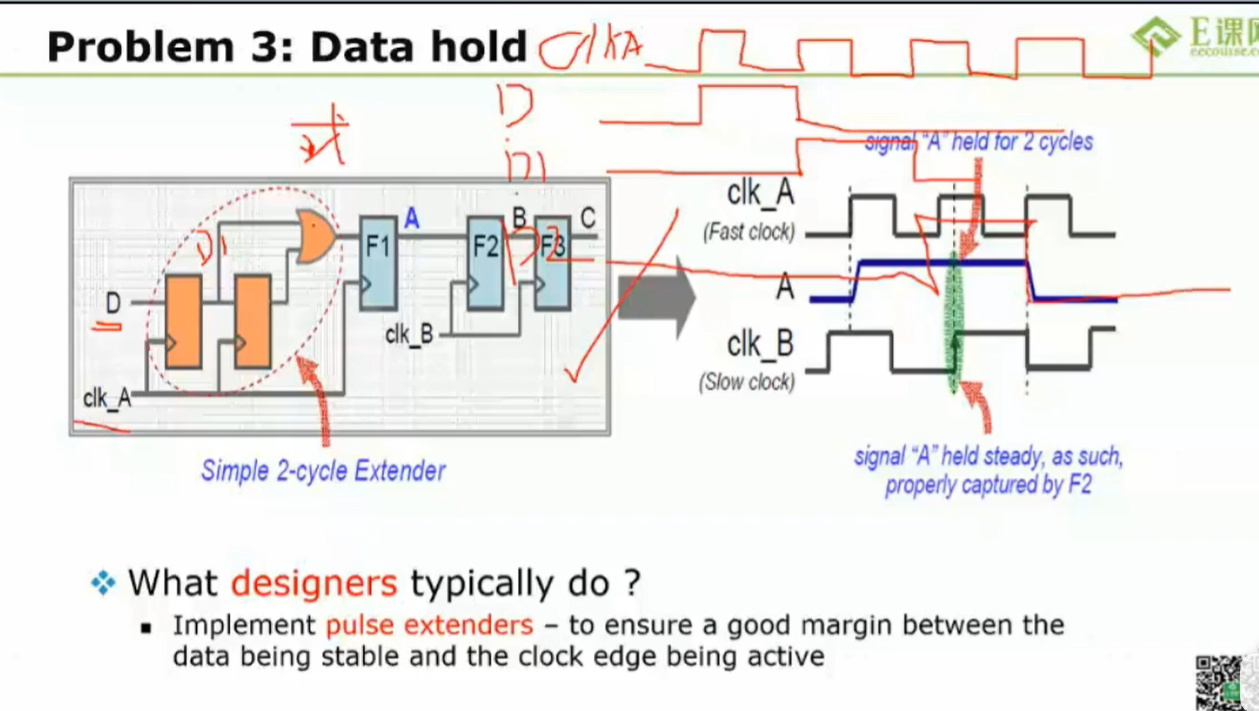

延时太长,建立时间和保持时间违例;

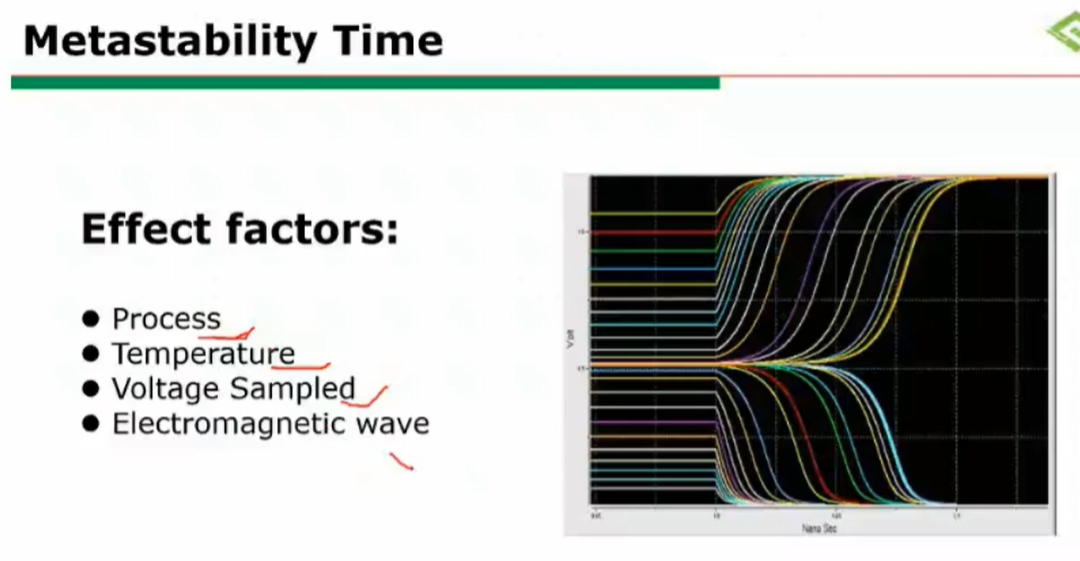

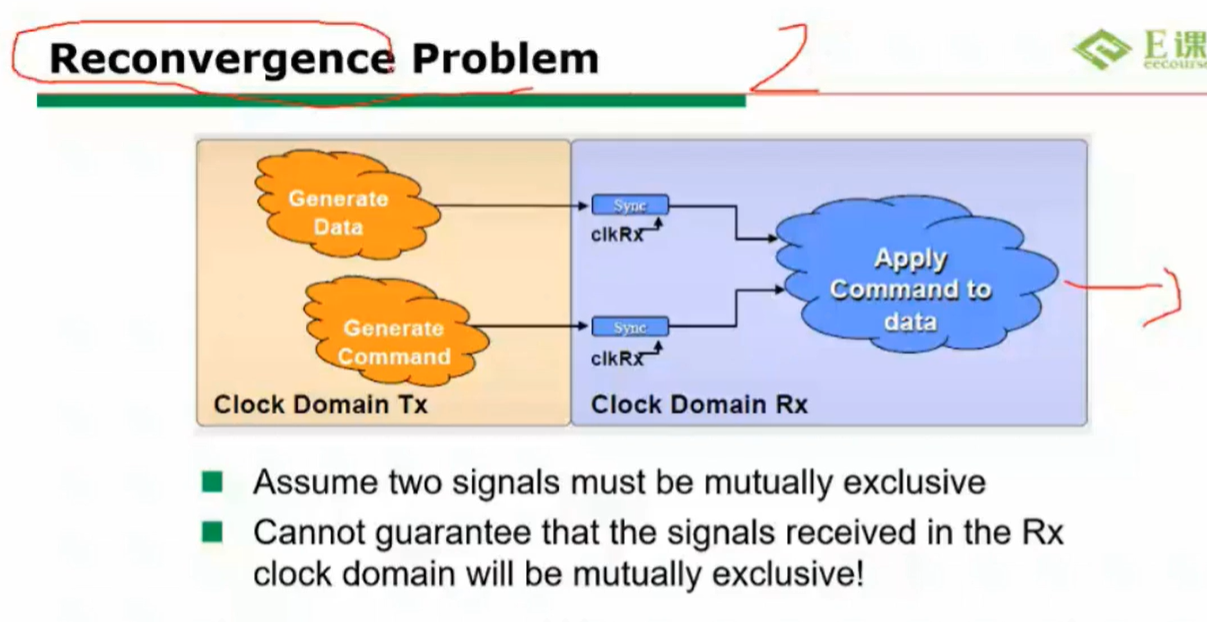

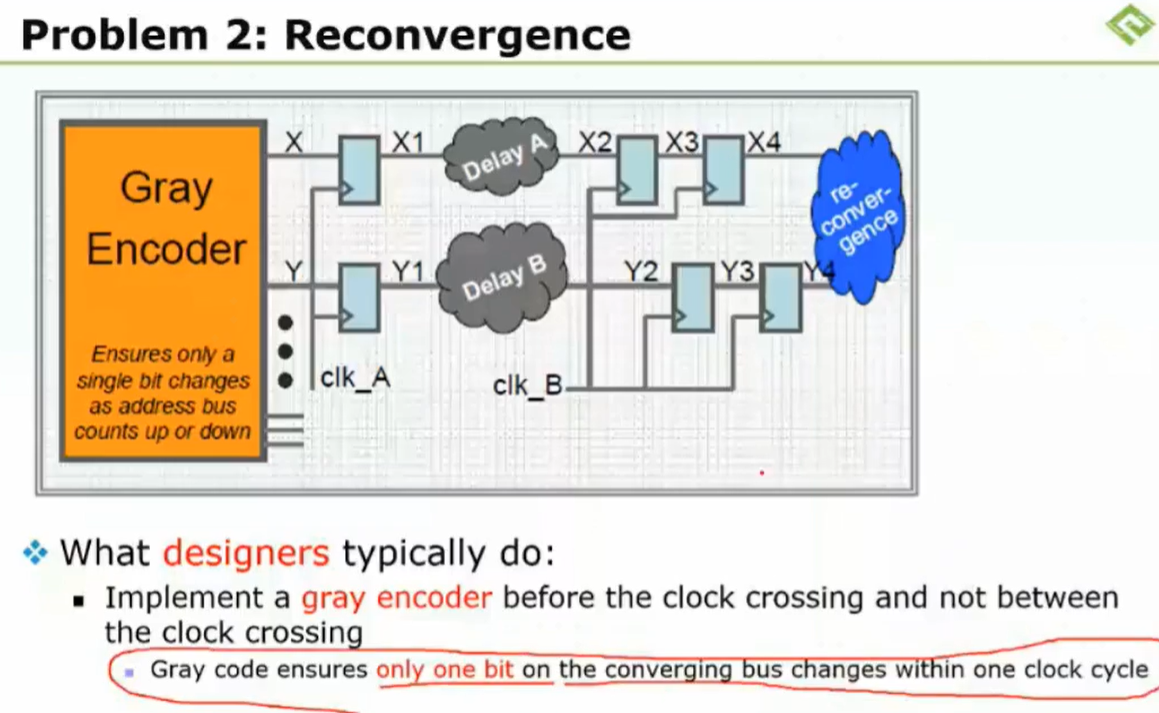

造成亚稳态,clock reconvergence pessimism是launching时钟路径和capturing时钟路径的延时差值,它发生在时钟切换的时候,是基于library通过查找LUT得到的

- 空白目录

- 任务01:数字IC设计流程_

- 任务02:数字前端设计工程师就业班概述_

- 任务03:VNC服务器使用说明_

- 任务07:数字电路基础_

- 任务09:逻辑综合工具Design Compiler的使用_

- 任务10:数字电路基础-时序逻辑基础

- 任务20: 经典组合和数字电路的设计_

- 任务21:有限状态机的写法_

- 任务25:CDC_Metastability(亚稳态)_

- 任务22:同步fifo-异步fifo的设计_

- 任务23:同步FIFO设计方法2介绍与仿真

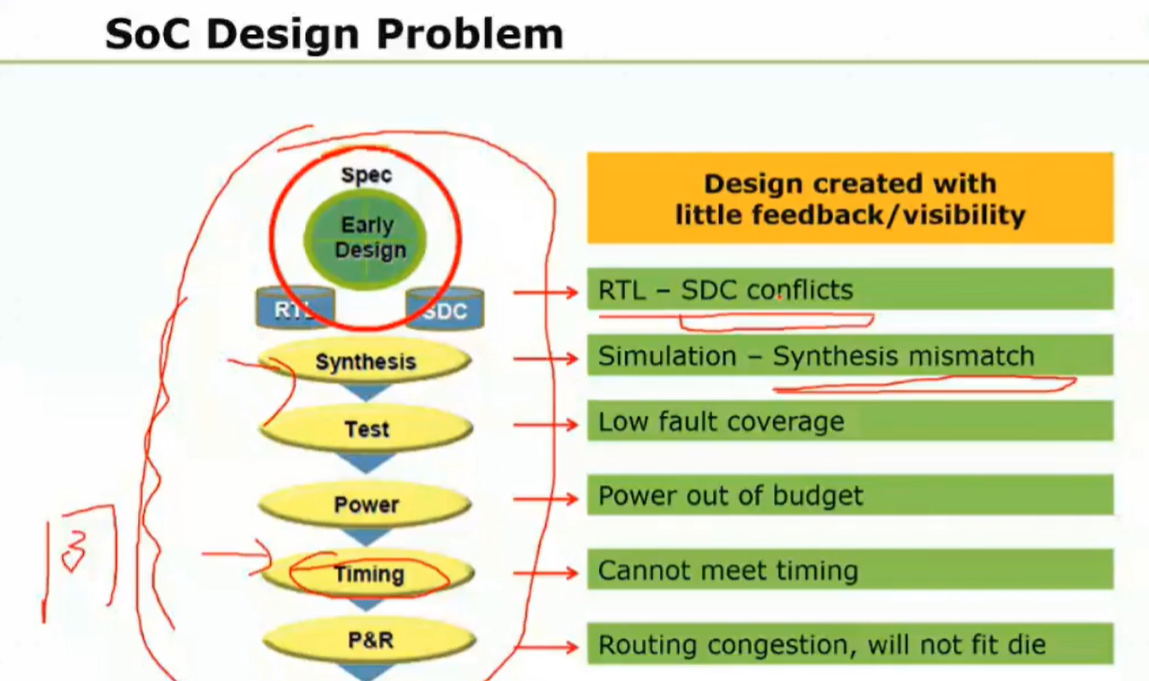

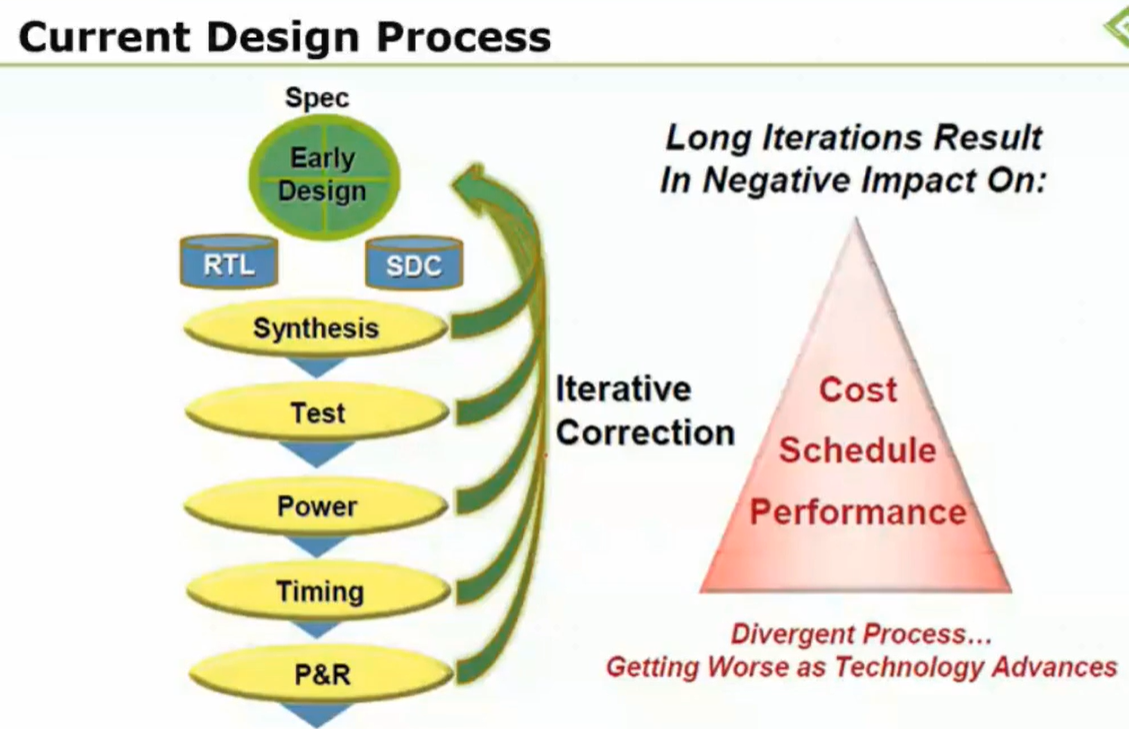

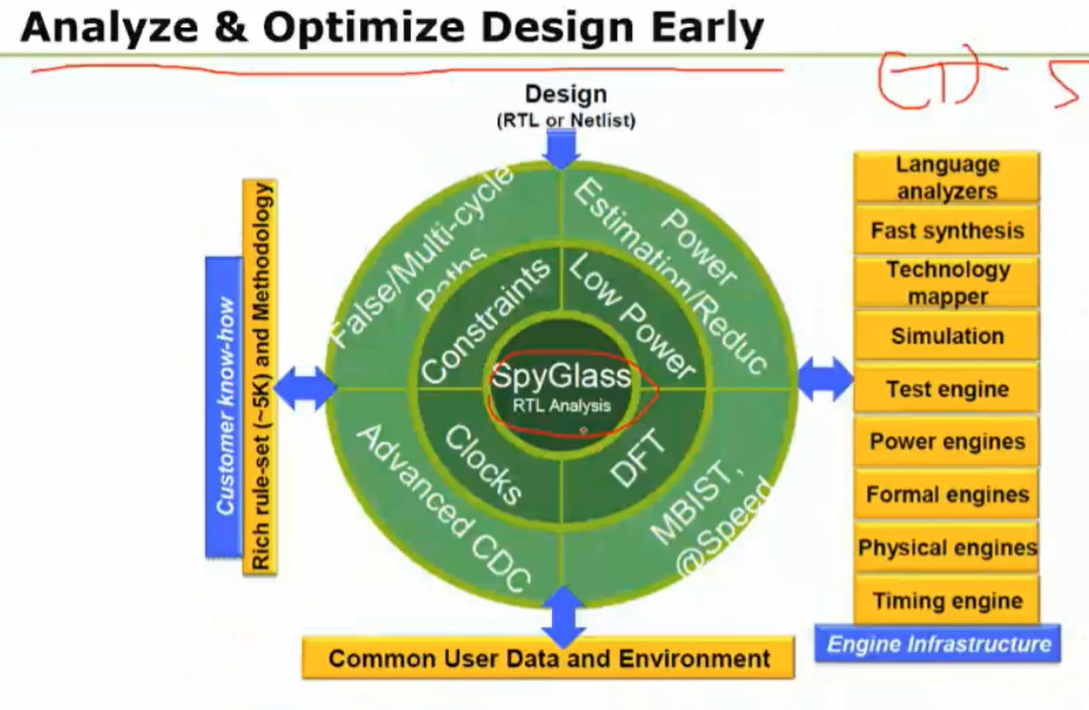

- 任务28:Spyglass的基础使用_

- 任务24:异步FIFO的设计_

- 任务29:Spyglass的基本使用-2_

- 任务11:逻辑仿真工具VCS的使用-Makefile_

- 任务15:Verilog Systemverilog - 数据类型_

- 任务13:逻辑综合工具-DC实操